# EPSON

# SED157A Series Dot Matrix LCD Driver

- Support up to 65×224 Display

Duits in Douter Supply Circuit for LC

- Built-in Power Supply Circuit for LCD

## ■ OVERVIEW

The SED157A Series is a single-chip dot matrix liquid crystal display driver that can be connected directly to a microprocessor bus. Eight-bit parallel or serial display data transmitted from the microprocessor is stored in the internal display data RAM, and the chip generates liquid crystal drive signals, independently of the microprocessor.

It has a on-chip  $65 \times 256$ -bit display data RAM, and there is a one-to-one correspondence between the dot pixel on the liquid crystal panel pixels and internal RAM bit. This feature ensures implementation of highly free display.

The SED157A Series incorporate 65 common output circuits and 224 segment output circuits. A single chip can drive a  $65 \times 224$  dot display (capable of displaying 14 columns  $\times$  4 rows with 16  $\times$  16-dot kanji font). Further, display capacity can be extended by designing two chips in a master/display configuration.

The SED157A Series can read and write RAM data with the minimum current consumption because it does not require any external operation clock. Also it incorporates a LCD power supply featuring a very low current consumption, a LCD drive power voltage regulator resistor and a display clock CR oscillator circuit. This allows the display system of a high-performance for handy equipment to be realized at the minimum power consumption and minimum component configuration.

## ■ FEATURES

- Direct display of RAM data using the display data RAM

- RAM bit data "1" ..... goes on.

"0" ..... goes off (at display normal rotation).

- RAM capacity

- $65 \times 256 = 16,640$  bits

- Liquid crystal drive circuit

65 circuits for the common output and 224 circuits for the segment output

- High-speed 8-bit MPU interface (Both the 80 and 68 series MUPs can directly be connected.)/serial interface enabled

- Abundant command functions

Display Data Read/Write, Display ON/OFF, Display Normal Rotation/Reversal, Page Address Set, Display Start Line Set, column address set, Status Read, Power Supply Save Display All Lighting ON/OFF, LCD Bias Set, Read Modify Write, Segment Driver Direction Select, Electronic Control, V5 Voltage Adjusting Built-in Resistance Ratio Set, Static Indicator, n Line Alternating Current Reversal Drive, Common Output State Selection, and Built-in Oscillator Circuit ON

• Built-in static drive circuit for indicators (One set, blinking speed variable)

## **SED157A Series**

- Built-in power supply circuit for low power supply liquid crystal drive Booster circuit (Boosting magnification - double, triple, quadruple, boosting reference power supply external input enabled)

- 3% high accuracy alternating current voltage adjusting circuit (Temperature gradient: -0.05%/°C)

Built-in V5 voltage adjusting resistor, built-in V1 to V4 voltage generation split resistors, built-in electronic control function, and voltage follower

- Built-in CR oscillator circuit (external clock input enabled)

- Ultra-low power consumption

- Power supplies

Logic power supply: VDD - VSS = 1.8 to 5.5 V Boosting reference power supply: VDD - VSS = 1.8 to 6.0 V Liquid crystal drive power supply: V5 - VDD = -4.5 to -18.0 V

- Wide operating temperature range -40 to 85°C

- CMOS process

- Shipping form Bare chip, TCP

- No light-resistant and radiation-resistant design are provided.

#### Series specification

| Product name | Duty | Bias     | SEG Dr | COM Dr | VREG temperature<br>gradient | Shipping form |

|--------------|------|----------|--------|--------|------------------------------|---------------|

| SED157AD0B   | 1/65 | 1/9, 1/7 | 224    | 65     | −0.05%/°C                    | Bare chip     |

| SED157ATo*   | 1/65 | 1/9, 1/7 | 224    | 65     | −0.05%/°C                    | TCP           |

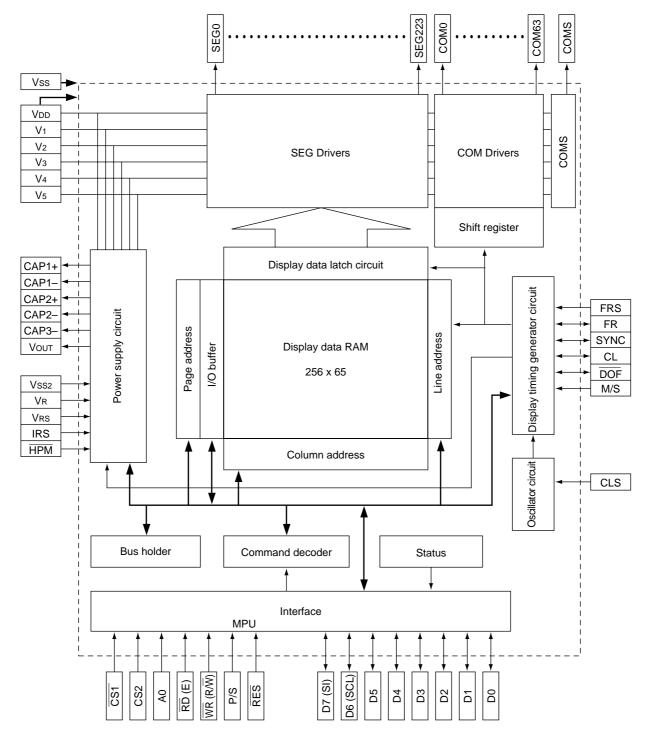

## BLOCK DIAGRAM

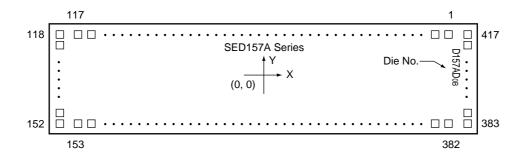

## ■ PIN ASSIGNMENT

Chip Specification

|              | Item              | x     | Size      | Y    | Unit |

|--------------|-------------------|-------|-----------|------|------|

| Chip size    |                   | 16.65 | ×         | 2.90 | mm   |

| Chip thickne | SS                |       | 0.625     |      | mm   |

| Bump pitch   |                   |       | 69 (Min.) |      | μm   |

| Bump size    | PAD No.1 to 117   | 85    | ×         | 85   | μm   |

|              | PAD No.118        | 85    | ×         | 73   | μm   |

|              | PAD No.119 to 151 | 85    | ×         | 47   | μm   |

|              | PAD No.152        | 85    | ×         | 73   | μm   |

|              | PAD No.153        | 73    | ×         | 85   | μm   |

|              | PAD No.154 to 381 | 47    | ×         | 85   | μm   |

|              | PAD No.382        | 73    | ×         | 85   | μm   |

|              | PAD No.383        | 86    | ×         | 73   | μm   |

|              | PAD No.384 to 416 | 85    | ×         | 47   | μm   |

|              | PAD No.417        | 85    | ×         | 73   | μm   |

| Bump heigh   | t                 |       | 17 (Typ.) |      | μm   |

## **EPSON**

## ■ PIN DESCRIPTION

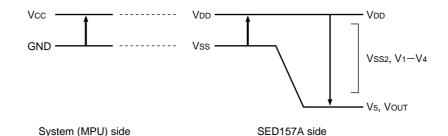

Power Supply Pin

| Pin name               | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Number of pins |

|------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Vdd                    | Power<br>supply | Commonly used with the MPU power supply pin Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12             |

| Vss                    | Power<br>supply | 0 V pin connected to the system ground (GND)                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9              |

| VSS2                   | Power<br>supply | Boosting circuit reference power supply for liquid crystal drive                                                                                                                                                                                                                                                                                                                                                                                                                  | 5              |

| Vrs                    | Power<br>supply | External input pin for liquid crystal power supply voltage<br>adjusting circuit<br>They are set to OPEN                                                                                                                                                                                                                                                                                                                                                                           | 2              |

| V1, V2<br>V3, V4<br>V5 | Power<br>supply | Multi-level power supply for liquid crystal drive. The voltage specified according to liquid crystal cells is impedance-converted by a split resistor or operation amplifier (OP amp) and applied.<br>The potential needs to be specified based on VDD to establish the relationship of dimensions shown below:                                                                                                                                                                   | 10             |

|                        |                 | $\begin{array}{c} \text{VDD} (=\!V0) \geq V1 \geq V2 \geq V3 \geq V4 \geq V5 \\ \text{Master operation}  \text{When the power supply is ON, the following voltages are applied to V1 ~ V4 from the built-in power supply circuit. The selection of the voltages is determined using the LCD bias set command. \\ \hline V1 & 1/9 \cdot V5 & 1/7 \cdot V5 \\ V2 & 2/9 \cdot V5 & 2/7 \cdot V5 \\ V3 & 7/9 \cdot V5 & 5/7 \cdot V5 \\ V4 & 8/9 \cdot V5 & 6/7 \cdot V5 \end{array}$ |                |

## • LCD Power Supply Circuit Pin

| Pin name | I/O | Description                                                                                                                                                                                                                                        | Number of pins |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CAP1+    | 0   | Boosting capacitor positive side connecting pin. Connects a capacitor between the pin and CAP1– pin.                                                                                                                                               | 2              |

| CAP1-    | 0   | Boosting capacitor negative side connecting pin. Connects a capacitor between the pin and CAP1+ pin.                                                                                                                                               | 2              |

| CAP2+    | 0   | Boosting capacitor positive side connecting pin. Connects a capacitor between the pin and CAP2– pin.                                                                                                                                               | 2              |

| CAP2-    | 0   | Boosting capacitor negative side connecting pin. Connects a capacitor between the pin and CAP2+ pin.                                                                                                                                               | 2              |

| CAP3–    | 0   | Boosting capacitor negative side connecting pin. Connects a capacitor between the pin and CAP1+ pin.                                                                                                                                               | 2              |

| Vout     | 0   | Boosting output pin. Connects a capacitor between the pin and Vss2.                                                                                                                                                                                | 2              |

| VR       | Ι   | Voltage adjusting pin. Applies voltage between VDD and V5 using a split resistor. Valid only when the V5 voltage adjusting built-in resistor is not used (IRS="L") Do not use VR when the V5 voltage adjusting built-in resistor is used (IRS="H") | 1              |

## • System Bus Connecting Pins

| Pin name                  | I/O |                                                                                      |                                                                                                                                                                                    | Descriptio                                                                | n                                                                             |                 |            | Number of<br>pins |

|---------------------------|-----|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------|------------|-------------------|

| D7 to D0<br>(SI)<br>(SCL) | I/O | MPU data bus<br>When the seria<br>D7: Serial da<br>D6: Serial clo<br>In this case, D | al interface is<br>ta entry pin (S<br>ock input pin (<br>0 to D5 are se                                                                                                            | selected (P/S<br>SI)<br>SCL)<br>et to high impe                           |                                                                               |                 |            | 8                 |

| AO                        | I   | discriminate da<br>A0="H": Indic                                                     | ata / comman<br>ates that D0 t                                                                                                                                                     |                                                                           |                                                                               | connected to    |            | 1                 |

| RES                       | Ι   | Initialized by se<br>Reset operation                                                 | etting RES to<br>n is performe                                                                                                                                                     | "L".<br>d at the RES                                                      | signal level.                                                                 |                 |            | 1                 |

| CS1<br>CS2                | I   |                                                                                      | nal. When C                                                                                                                                                                        | S1="L" and C                                                              | S2="H", this sig                                                              | nal becomes a   | ctive      | 2                 |

| RD<br>(E)                 | I   | When the 80  Pin that conn  the SED157A                                              | series M <u>PU</u> i<br>ects the RD s<br>series data b<br>series MPU i                                                                                                             | s connected, a<br>signal of the 80<br>ous is set in the<br>s connected, a | active "L" is set.<br>) series MPU. V<br>e output state.<br>active "H" is set | Vhen this signa | al is "L", | 1                 |

| WR<br>(R/W)               | I   | Pin that conn                                                                        | ects the WR s<br>e leading edg<br>series MPU is<br>ontrol signal ir<br>ad operation                                                                                                | signal of <u>the</u> 8<br>e of the WR s<br>s connected,                   | active "L" is set.<br>0 series MPU.<br>ignal.                                 |                 | ignal is   | 1                 |

| FRS                       | 0   | Output pin for Used together                                                         | static drive<br>with the SYN                                                                                                                                                       | C pin                                                                     |                                                                               |                 |            | 1                 |

| C86                       | I   | MPU interface<br>C86="H": 68<br>C86="L": 80 s                                        | series MPU ir                                                                                                                                                                      | nterface                                                                  |                                                                               |                 |            | 1                 |

| P/S                       | I   | P/S="H": Paral<br>P/S="L": Serial                                                    | Switching pin for parallel data entry/serial data entry<br>P/S="H": Parallel data entry<br>P/S="L": Serial data entry<br>According to the P/S state, the following table is given. |                                                                           |                                                                               |                 |            |                   |

|                           |     | P/S                                                                                  | Data/<br>command                                                                                                                                                                   | Data                                                                      | Read/write                                                                    | Serial clock    |            |                   |

|                           |     | "H"                                                                                  | A0                                                                                                                                                                                 | D0 to D7                                                                  | $\overline{RD}, \overline{WR}$                                                |                 |            |                   |

|                           |     | "L"                                                                                  | A0                                                                                                                                                                                 | SI (D7)                                                                   | Write-only                                                                    | SCL (D6)        |            |                   |

|                           |     | <u>be</u> "H", "L", <u>or</u><br>RD(E) and WF                                        | OPEN".<br>(R/W) are fix                                                                                                                                                            | ked to "H" or "                                                           | npedance. D0 t<br>L".<br>a cannot be rea                                      |                 |            |                   |

| Pin name | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Number of<br>pins |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| CLS      | I    Pin that selects the validity/invalidity of the built-in oscillator circuit for display clocks.      CLS="H": Built-in oscillator circuit valid      CLS="L": Built-in oscillator circuit invalid (external input)      When CLS="L". display clocks are input from the CL pin.      When the SED157A series is used for the master/slave configuration, each of the CLS pins is set to the same level together.      Display clock    Master      Built-in oscillator circuit used    "H"      External input    "L" |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |  |  |  |  |

| M/S      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin that selects the master/slave operation for the SED157A series.The liquid crystal display system is synchronized by outputting the timing signalrequired for the liquid crystal display for the master operation and inputting thetiming signal required for the liquid crystal display for the master operation and inputting theM/S="H": Master operationM/S="H": Master operationM/S="H": Slave operationAccording to the M/S and CLS states, the following table is given.M/SCLFRSYNCFRSDOF | 1                 |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | circuit      circuit        "H"      "H"      Valid      Output      Output      Output                                                                                                                                                                                                                                                                                                                                                                                                             |                   |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | "L"InvalidValidInputOutputOutputOutputOutput"L""H"InvalidInvalidInputInputInputInputInput"L"InvalidInvalidInputInputInputInputInput                                                                                                                                                                                                                                                                                                                                                                 |                   |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Display clock I/O pin<br>According to the M/S and CLS states, the following table is given.<br>M/S    CLS    CL      "H"    "H"    Output      "L"    Input                                                                             |                   |  |  |  |  |

| FR       | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Liquid crystal alternating current signal I/O pin<br>M/S="H": Output<br>M/S="L": Input<br>When the SED157A series is used for the master/slave configuration, each<br>FR pin is connected.                                                                                                                                                                                                                                                                                                          | 1                 |  |  |  |  |

| SYNC     | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Liquid crystal synchronizing current signal I/O pin<br>M/S="H": Output<br>M/S="L": Input<br>When the SED157A series is used for the master/slave configuration, each<br>SYNC pin is connected.                                                                                                                                                                                                                                                                                                      | 2                 |  |  |  |  |

| DOF      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Liquid crystal display blanking control pin<br>M/S="H": Output<br>M/S="L": Input<br>When the SED157A series is used for the master/slave configuration, each<br>DOF pin is connected.                                                                                                                                                                                                                                                                                                               |                   |  |  |  |  |

| IRS      | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V5 voltage adjusting resistor selection pin<br>IRS="H": Built-in resistor used<br>IRS="L": Built-in resistor not used. The V5 voltage is adjusted by<br>the VR pin and stand-alone split resistor.<br>Valid only at master operation. The pin is fixed to "H" or "L" at slave operation.                                                                                                                                                                                                            | 1                 |  |  |  |  |

| HPM      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Power supply control pin of the power supply circuit for liquid<br>crystal drive<br>HPM="H": Normal mode<br>HPM="L": High power supply mode<br>Valid only at master operation. The pin is fixed to "H" or "L" at slave operation.                                                                                                                                                                                                                                                                   | 1                 |  |  |  |  |

## • Liquid Crystal Drive Pin

| Pin name   | I/O                 | Description                                                                         |                         |                                              |                                         |               |     |  |

|------------|---------------------|-------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|-----------------------------------------|---------------|-----|--|

| SEG0<br>to | 0                   | Output pins for the signal are combined                                             | LCD segm<br>d to select | ent drive. Contents on a desired level amon  | of the display RAM<br>g VDD, V2, V3 and | and FR<br>V5. | 224 |  |

| SEG223     |                     |                                                                                     |                         | Output                                       | voltage                                 | ]             |     |  |

|            |                     | RAM data                                                                            | FR                      | Display<br>normal operation                  | Display reversal                        | ]             |     |  |

|            |                     | Н                                                                                   | Н                       | Vdd                                          | V2                                      |               |     |  |

|            |                     | Н                                                                                   | L                       | V5                                           | V3                                      | -             |     |  |

|            |                     | L                                                                                   | Н                       | V2                                           | Vdd                                     | -             |     |  |

|            | LV3V5Power save—VDD | L                                                                                   | L                       | V3                                           | V5                                      |               |     |  |

|            |                     |                                                                                     |                         |                                              |                                         |               |     |  |

| COM0<br>to |                     | Output pins for the to select a desired                                             | LCD comn<br>evel amon   | non drive. Scan data<br>g VDD, V1, V4 and V5 | and FR signal are                       | combined      | 64  |  |

| COM63      |                     | Scanning                                                                            | data                    | FR                                           | Output voltage                          |               |     |  |

|            |                     | Н                                                                                   |                         | Н                                            | V5                                      |               |     |  |

|            |                     | Н                                                                                   |                         | L                                            | Vdd                                     |               |     |  |

|            |                     | L                                                                                   |                         | Н                                            | V1                                      |               |     |  |

|            |                     | L                                                                                   |                         | L                                            | V4                                      |               |     |  |

|            |                     | Power s                                                                             | ave                     | —                                            | Vdd                                     |               |     |  |

| COMS       | 0                   | Indicator dedicated<br>Set to OPEN when<br>When COMS is use<br>to both the master a | not used<br>d for the n | out pin<br>naster/slave configura            | ation, the same sig                     | nal is output | 2   |  |

#### • Test Pin

| Pin name                | I/O | Description                                                                                                             | Number of<br>pins |

|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------|-------------------|

| TEST1 to 4, 10 to 13    | I/O | IC chip test pin. Fix the pin to "H".                                                                                   | 8                 |

| TEST5 to<br>9, 14 to 16 | I/O | IC chip test pin. Take into consideration so that the capacity of lines cannot be exhausted by setting the pin to OPEN. | 13                |

## ■ ABSOLUTE MAXIMUM RATINGS

| Vss=0 V | unless   | specified | otherwise   |

|---------|----------|-----------|-------------|

|         | 41110000 | opeeniea  | 01110111100 |

| Item                         | l                     | Symbol         | Specif | icatio | on value | Unit |

|------------------------------|-----------------------|----------------|--------|--------|----------|------|

| Power supply voltage         |                       | Vdd            | -0.3   | to     | +7.0     | V    |

| Power supply voltage (2)     |                       |                | -7.0   | to     | +0.3     |      |

| (Based on VDD)               | At triple boosting    | Vss2           | -6.0   | to     | +0.3     |      |

|                              | At quadruple boosting |                | -4.5   | to     | +0.3     |      |

| Power supply voltage (3) (Ba | sed on Vdd)           | V5, Vout       | -22.0  | to     | +0.3     |      |

| Power supply voltage (4) (Ba | sed on Vdd)           | V1, V2, V3, V4 | V5     | to     | +0.3     |      |

| Input voltage                |                       | Vin            | -0.3   | to     | Vdd+0.3  |      |

| Output voltage               |                       | Vout           | -0.3   | to     | Vdd+0.3  |      |

| Operating temperature        | Operating temperature |                | -40    | to     | +85      | °C   |

| Storage temperature          | ТСР                   | TSTR           | -55    | to     | +100     |      |

|                              | Bare chip             |                | -55    | to     | +125     |      |

- Notes: 1. The values of the Vss<sub>2</sub>, V<sub>1</sub> to V<sub>5</sub>, and Vout voltages are based on VDD=0 V.

- 2. The V1, V2, V3, and V4 voltages must always satisfy the condition of  $VDD \ge V1 \ge V2 \ge V3 \ge V4 \ge V5$ .

- 3. Insure that voltage levels Vss₂ and Vou⊤ are always such that the relationship of VDD≥Vss≥Vss₂≥ Vou⊤ is maintained.

- 4. When LSI is used exceeding the absolute maximum ratings, the LSI may be damaged permanently. Besides, it is desirable that the LSI should be used in the electrical characteristics condition for normal operation. If this condition is exceeded, the LSI may malfunction and have an adverse effect on the reliability of the LSI.

## ■ DC Characteristics

Vss=0 V, Vdd=3.0 V  $\pm$  10%, and Ta=–40 to 85°C

|                       |                       |        | <b>A</b> 11/1       |           | Spe     | cification v |         | Applicable |           |

|-----------------------|-----------------------|--------|---------------------|-----------|---------|--------------|---------|------------|-----------|

|                       | ltem                  | Symbol | Conditio            | on        | Min.    | Тур.         | Max.    | Unit       | pin       |

| Operating voltage     | Recommended operation | Vdd    |                     |           | 2.7     | _            | 3.3     | V          | VDD       |

| (1)                   | Operable              | Vdd    |                     |           | 1.8     | _            | 5.5     |            | Vdd       |

| Operating voltage     | Recommended operation | VSS2   | (Based on VDD)      |           | -3.3    | —            | -2.7    |            | VSS2      |

| (2)                   | Operable              | Vss2   | (Based on VDD)      |           | -6.0    | —            | -1.8    |            | VSS2      |

| Operating             | Operable              | V5     | (Based on VDD)      |           | -18.0   | _            | -4.5    | 1          | V5        |

| voltage               | Operable              | V1, V2 | (Based on VDD)      |           | 0.4×V5  | —            | Vdd     |            | V1, V2    |

| (3)                   | Operable              | V3, V4 | (Based on VDD)      |           | V5      | —            | 0.6×V5  |            | V3, V4    |

| High level ir         | nput voltage          | VIHC   |                     |           | 0.8×Vdd | _            | Vdd     |            |           |

| Low level in          | put voltage           | VILC   |                     |           | Vss     | —            | 0.2×Vdd |            |           |

| High level o          | utput voltage         | Vонс   | Іон=–0.5mA          |           | 0.8×Vdd | _            | Vdd     |            |           |

| Low level ou          | utput voltage         | Volc   | lo∟=0.5mA           |           | Vss     | —            | 0.2×Vdd |            |           |

| Input leak c          | urrent                | lu     | VIN=VDD or Vss      |           | -1.0    | _            | 1.0     | μA         |           |

| Output leak           | current               | ILO    |                     |           | -3.0    | —            | 3.0     |            |           |

| Liquid crysta         | al driver             | Ron    | Ta=25°C             | V5=-14.0V |         | 2.0          | 3.5     | KΩ         | SEGn      |

| On resist             | tance                 |        | (Based on VDD)      | V5=-8.0V  | —       | 3.2          | 5.4     |            | COMn      |

| Static currer         | nt consumption        | Issq   |                     | •         | _       | 0.01         | 5       | μA         | Vss, Vss2 |

| Output leak           | current               | l5Q    | V5=-18.0V (Based on | Vdd)      | —       | 0.01         | 15      |            | V5        |

| Input pin ca          | pacity                | Сі     | Ta=25°C, f=1MHz     |           |         | 5.0          | 8.0     | pF         |           |

| Oscillating frequency | Built-in oscillation  | fosc   | Ta=25°C             |           | 18      | 22           | 26      | kHz        |           |

|                       | External input        | fc∟    |                     |           | 4.5     | 5.5          | 6.5     |            | CL        |

|            | lt a see                                       | Symbol |                                         | _              | Spe   | Specification value |       |      | Applicable |

|------------|------------------------------------------------|--------|-----------------------------------------|----------------|-------|---------------------|-------|------|------------|

|            | Item                                           | Symbol | Conditio                                | n              | Min.  | Тур.                | Max.  | Unit | pin        |

| circuit    | Input voltage                                  | Vss2   | At triple boosting<br>(Based on VDD)    |                | -6.0  | _                   | -1.8  | V    | Vss2       |

| supply ci  |                                                | Vss2   | At quadruple boosting<br>(Based on VDD) |                | -5.0  | —                   | -1.8  |      | Vss2       |

| Ins        | Boosting output voltage                        | Vout   | (Based on VDD)                          |                | -20.0 | —                   | _     | ]    | Vout       |

| power      | Voltage adjusting circuit<br>operating voltage | Vout   | (Based on VDD)                          |                | -20.0 | _                   | -6.0  |      | Vout       |

| Built-in p | V/F circuit operating voltage                  | V5     | (Based on VDD)                          | (Based on VDD) |       | —                   | -4.5  | 1    | V5         |

| ы          | Reference voltage                              | Vreg0  | Ta=25°C,                                | –0.05%/°C      | -2.04 | -2.10               | -2.16 | 1    |            |

11

Dynamic current consumption value (1) During display operation and built-in power supply OFF Current values dissipated by the whole IC when the external power supply is used

| Display | All | White |  |

|---------|-----|-------|--|

|---------|-----|-------|--|

| Display All White Ta |                  |                         |      |             |      |         |         |  |  |  |  |

|----------------------|------------------|-------------------------|------|-------------|------|---------|---------|--|--|--|--|

| Item Sy              | Symbol           | Condition               | Spec | ification v | Unit | Domorko |         |  |  |  |  |

|                      | Symbol Condition | Condition               | Min. | Тур.        | Max. | Unit    | Remarks |  |  |  |  |

| Dynamic current      | IDD              | VDD=5.0V, V5-VDD=-11.0V | —    | 25          | 42   | μA      |         |  |  |  |  |

| consumption          | (1)              | VDD=3.0V, V5-VDD=-11.0V | —    | 25          | 42   |         |         |  |  |  |  |

| Display Checker Pattern Ta=25°C |           |                         |             |        |         |      |         |  |  |  |

|---------------------------------|-----------|-------------------------|-------------|--------|---------|------|---------|--|--|--|

| Item Symbo                      | Condition | Spec                    | ification v | l lmit | Domorko |      |         |  |  |  |

|                                 | Symbo     | Condition               | Min.        | Тур.   | Max.    | Unit | Remarks |  |  |  |

| Dynamic current                 | IDD       | VDD=5.0V, V5-VDD=-11.0V | —           | 38     | 64      | μA   |         |  |  |  |

| consumption                     | (1)       | VDD=3.0V, V5-VDD=-11.0V | —           | 38     | 64      |      |         |  |  |  |

Dynamic current consumption value (2) During display operation and built-in power supply ON Current values dissipated by the whole IC containing the built-in power supply circuit

**Display Checker Pattern**

| ltom            | Cumb a | Condi              | Spec            | ification v | Unit | Remarks |      |         |

|-----------------|--------|--------------------|-----------------|-------------|------|---------|------|---------|

| Item            | Symbo  | Condi              | tion            | Min.        | Тур. | Max.    | Unit | Remarks |

| Dynamic current | IDD    | Vdd=5.0V,          | Normal mode     | _           | 92   | 154     | μA   |         |

| consumption     | (2)    | Triple boosting    |                 |             |      |         |      |         |

|                 |        | V5-VDD=-11.0V      | High power mode | _           | 242  | 405     | 1    |         |

|                 |        | Vdd=3.0V,          | Normal mode     |             | 129  | 216     |      |         |

|                 |        | Quadruple boosting |                 |             |      |         |      |         |

|                 |        | V5–Vdd=–11.0V      | High power mode | _           | 310  | 518     |      |         |

#### **Display Checker Pattern**

| ltom            | Sumbo | Conc               | Spec            | ification v | Unit | Remarks |      |         |

|-----------------|-------|--------------------|-----------------|-------------|------|---------|------|---------|

| Item            | Symbo | Conc               | attion          | Min.        | Тур. | Max.    | Unit | Remarks |

| Dynamic current | IDD   | Vdd=5.0V,          | Normal mode     | —           | 132  | 221     | μA   |         |

| consumption     | (2)   | Triple boosting    |                 |             |      |         |      |         |

|                 |       | V5-VDD=-11.0V      | High power mode | _           | 280  | 468     |      |         |

|                 |       | Vdd=3.0V,          | Normal mode     | _           | 167  | 279     |      |         |

|                 |       | Quadruple boosting |                 |             |      |         |      |         |

|                 |       | V5-VDD=-11.0V      | High power mode | _           | 350  | 585     |      |         |

Current consumption at power save <code>Vss=0V</code> and <code>Vdd= 3.0 V \pm 10%</code>

|                |        |           |      |             |      |          | Ta=25°C |

|----------------|--------|-----------|------|-------------|------|----------|---------|

| Item           | Symbol | Condition | Spec | ification v | Unit | Domorika |         |

|                |        |           | Min. | Тур.        | Max. | Unit     | Remarks |

| Sleep state    | IDDS1  |           | —    | 0.01        | 5    | μΑ       |         |

| Stand-by state | IDDS2  |           |      | 4           | 8    |          |         |

## **EPSON**

Ta=25°C

Ta=25°C

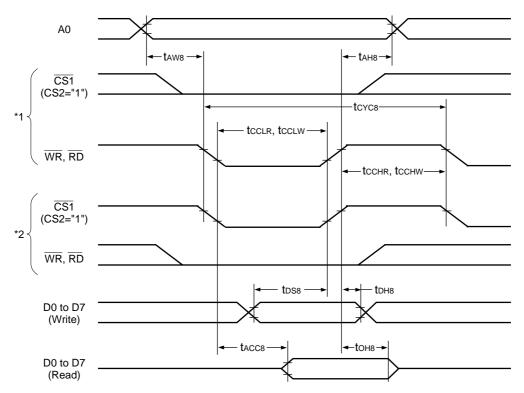

## ■ TIMING CHARACTERISTICS

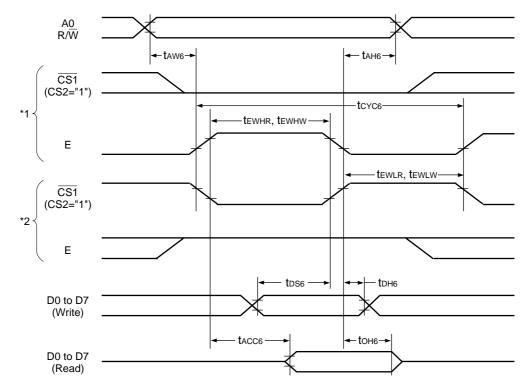

• System bus read/write characteristics 1 (80 series MPU)

|                            |          |               |           | <b>b</b> | to 5.5V, Ta=–∕<br><b>tion value</b> |      |

|----------------------------|----------|---------------|-----------|----------|-------------------------------------|------|

| Item                       | Signal   | Symbol        | Condition | Min.     | Max.                                | Unit |

| Address hold time          | A0       | tAH8          |           | 0        | _                                   | ns   |

| Address setup time         |          | tAW8          |           | 0        | _                                   |      |

| System cycle time          | A0       | tCYC8         |           | 333      | —                                   |      |

| Control L pulse width (WR) | WR       | tCCLW         |           | 30       | —                                   |      |

| Control L pulse width (RD) | RD       | tCCLR         |           | 70       | _                                   |      |

| Control H pulse width (WR) | WR       | tcchw         |           | 30       | _                                   |      |

| Control H pulse width (RD) | RD       | <b>t</b> CCHR |           | 30       | —                                   |      |

| Data setup time            | D0 to D7 | tDS8          |           | 30       | _                                   |      |

| Data hold time             |          | tDH8          |           | 10       | —                                   |      |

| RD access time             |          | tACC8         | CL=100pF  |          | 70                                  |      |

| Output disable time        |          | tOH8          |           | 5        | 50                                  |      |

[VDD=2.7V to 4.5V. Ta=-40 to 85°C]

|                            | <u>.</u> |               | Condition | Specifica | tion value |      |

|----------------------------|----------|---------------|-----------|-----------|------------|------|

| Item                       | Signal   | Symbol        |           | Min.      | Max.       | Unit |

| Address hold time          | A0       | tah8          |           | 0         | _          | ns   |

| Address setup time         |          | tAW8          |           | 0         |            |      |

| System cycle time          | A0       | tCYC8         |           | 500       | —          |      |

| Control L pulse width (WR) | WR       | tCCLW         |           | 60        |            |      |

| Control L pulse width (RD) | RD       | tCCLR         |           | 120       | _          |      |

| Control H pulse width (WR) | WR       | tCCHW         |           | 60        | _          |      |

| Control H pulse width (RD) | RD       | <b>t</b> CCHR |           | 60        | —          |      |

| Data setup time            | D0 to D7 | tDS8          |           | 40        | _          |      |

| Data hold time             |          | tdh8          |           | 15        |            |      |

| RD access time             |          | tACC8         | CL=100pF  | —         | 140        |      |

| Output disable time        |          | tOH8          |           | 10        | 100        |      |

[VDD=1.8V to 2.7V, Ta=-40 to 85°C]

|                            | <u>.</u> |        |           | Specification value |      |      |

|----------------------------|----------|--------|-----------|---------------------|------|------|

| Item                       | Signal   | Symbol | Condition | Min.                | Max. | Unit |

| Address hold time          | A0       | tah8   |           | 0                   |      | ns   |

| Address setup time         |          | tAW8   |           | 0                   | —    |      |

| System cycle time          | A0       | tCYC8  |           | 1000                | —    |      |

| Control L pulse width (WR) | WR       | tCCLW  |           | 120                 | _    |      |

| Control L pulse width (RD) | RD       | tCCLR  |           | 240                 | —    |      |

| Control H pulse width (WR) | WR       | tCCHW  |           | 120                 | —    |      |

| Control H pulse width (RD) | RD       | tCCHR  |           | 120                 |      |      |

| Data setup time            | D0 to D7 | tDS8   |           | 80                  | —    |      |

| Data hold time             |          | tDH8   |           | 30                  | —    |      |

| RD access time             |          | tACC8  | CL=100pF  |                     | 280  |      |

| Output disable time        |          | tOH8   |           | 10                  | 200  |      |

Notes: 1. This is the case of accessing by  $\overline{WR}$  and  $\overline{RD}$  when  $\overline{CS1}$  = "L". 2. This is the case of accessing by  $\overline{CS1}$  when  $\overline{WR}$  and  $\overline{RD}$  = "L".

The rise and fall times (tr and tr) of the input signal are specified for less than 15 ns. When using the system cycle time at high speed, they are specified for (tr+tf) ≤ (tCYC8–tCCLW–tCCHW) or (tr+tf) ≤ (tCYC8–tCCLR–tCCHR). 4. All timings are specified based on the 20 and 80% of VDD.

5.tccLW and tccLR are specified for the overlap period when  $\overline{CS1}$  is at "L" (CS2= "H") level and  $\overline{WR}$ ,  $\overline{RD}$  are at the "L" level.

## • System bus read/write characteristics 2 (68 series MPU)

|                      |       |          |          | r              | [VDD=4.5V 1 | to 5.5V, Ta=–4 | 10 to 85°C] |

|----------------------|-------|----------|----------|----------------|-------------|----------------|-------------|

|                      |       | Signal   | Complete | O a mallitha m | Specifica   | tion value     |             |

| Item                 |       | Signal   | Symbol   | Condition      | Min.        | Max.           | Unit        |

| Address hold time    |       | A0       | tAH6     |                | 0           | _              | ns          |

| Address setup time   |       |          | tAW6     |                | 0           | —              |             |

| System cycle time    |       |          | tCYC6    |                | 333         | —              |             |

| Data setup time      |       | D0 to D7 | tDS6     |                | 30          | _              |             |

| Data hold time       |       |          | tDH6     |                | 10          | —              |             |

| Access time          |       |          | tACC6    | CL=100pF       | _           | 70             |             |

| Output disable time  |       |          | tOH6     |                | 10          | 50             |             |

| Enable H pulse width | Read  | E        | tewhr    |                | 70          | _              |             |

|                      | Write |          | tewhw    |                | 30          | —              |             |

| Enable L pulse width | Read  | E        | tEWLR    |                | 30          | _              |             |

|                      | Write |          | tEWLW    |                | 30          | _              |             |

#### [VDD=2.7V to 4.5V, Ta=-40 to 85°C]

| lt a m               |       | 0:       | 0 miles l | O a malifilia m | Specifica | tion value | 11   |

|----------------------|-------|----------|-----------|-----------------|-----------|------------|------|

| Item                 |       | Signal   | Symbol    | Condition       | Min.      | Max.       | Unit |

| Address hold time    |       | A0       | tAH6      |                 | 0         | —          | ns   |

| Address setup time   |       |          | tAW6      |                 | 0         | _          |      |

| System cycle time    |       |          | tCYC6     |                 | 500       | —          |      |

| Data setup time      |       | D0 to D7 | tDS6      |                 | 40        | —          |      |

| Data hold time       |       |          | tDH6      |                 | 15        | _          |      |

| Access time          |       |          | tACC6     | CL=100pF        | —         | 140        |      |

| Output disable time  |       |          | tOH6      |                 | 10        | 100        |      |

| Enable H pulse width | Read  | E        | tewhr     |                 | 120       | —          |      |

|                      | Write |          | tewhw     |                 | 60        | _          |      |

| Enable L pulse width | Read  | E        | tewlr     |                 | 60        | _          |      |

|                      | Write |          | tewlw     |                 | 60        | _          |      |

#### [VDD=1.8V to 2.7V, Ta=-40 to 85°C]

| literes              |       | Signal Symbol | Cumb al | Condition | Specifica | tion value | Unit |

|----------------------|-------|---------------|---------|-----------|-----------|------------|------|

| Item                 |       | Signal Symbol |         | Condition | Min.      | Max.       | Unit |

| Address hold time    |       | A0            | tAH6    |           | 0         | —          | ns   |

| Address setup time   |       |               | tAW6    |           | 0         | _          |      |

| System cycle time    |       |               | tCYC6   |           | 1000      | —          |      |

| Data setup time      |       | D0 to D7      | tDS6    |           | 80        | —          |      |

| Data hold time       |       |               | tDH6    |           | 30        | _          |      |

| Access time          |       |               | tACC6   | CL=100pF  | —         | 280        |      |

| Output disable time  |       |               | tOH6    |           | 10        | 200        |      |

| Enable H pulse width | Read  | E             | tewhr   |           | 240       | —          |      |

|                      | Write |               | tewhw   |           | 120       | —          |      |

| Enable L pulse width | Read  | E             | tewlr   |           | 120       | —          |      |

|                      | Write |               | tewlw   |           | 120       |            |      |

Notes: 1. This is the case of accessing by <u>E</u> when  $\overline{CS1} = "L"$ .

2. This is the case of accessing by CS1 when E = "H". 3. The rise and fall times (tr and tr) of the input signal are specified for less than 15 ns. When using the system cycle time at high speed, they are specified for  $(tr+tf) \le (tCYC6-tEWLW-tEWHW)$  or  $(tr+tf) \le (tCYC6-tEWLR-tEWHR)$ .

4. All timings are specified based on the 20 and 80% of VDD.

5. tEWLW and tEWLR are specified for the overlap period when  $\overline{CS1}$  is at "L" (CS2 = "H") level and E is at the "H" level.

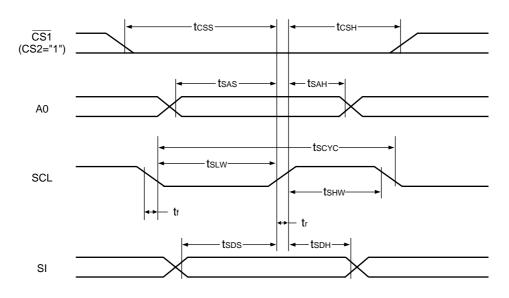

#### Serial interface

#### [VDD=4.5V to 5.5V, Ta=-40 to 85°C]

| ltem                | Signal | Symbol       | Condition | Specification value |      | Unit |

|---------------------|--------|--------------|-----------|---------------------|------|------|

|                     | Signal | Symbol       |           | Min.                | Max. |      |

| Serial clock cycle  | SCL    | tSCYC        |           | 200                 | —    | ns   |

| SCL "H" pulse width |        | tshw         |           | 75                  |      |      |

| SCL "L" pulse width |        | tSLW         |           | 75                  |      |      |

| Address setup time  | A0     | tsas         |           | 50                  | —    | 1    |

| Address hold time   |        | <b>t</b> SAH |           | 100                 |      |      |

| Data setup time     | SI     | tSDS         |           | 50                  | —    | ]    |

| Data hold time      |        | <b>t</b> SDH |           | 50                  |      |      |

| CS-SCL time         | CS     | tcss         |           | 100                 | —    | ]    |

|                     |        | tCSH         |           | 100                 |      |      |

#### [VDD=2.7V to 4.5V, Ta=-40 to 85°C]

|                     |        |        |           | Creation  | Unit |      |

|---------------------|--------|--------|-----------|-----------|------|------|

| Item                | Signal | Symbol | Condition | Specifica |      |      |

|                     | Signal | Symbol |           | Min.      | Max. | Onic |

| Serial clock cycle  | SCL    | tSCYC  |           | 250       | —    | ns   |

| SCL "H" pulse width |        | tshw   |           | 100       | _    |      |

| SCL "L" pulse width |        | tSLW   |           | 100       | _    |      |

| Address setup time  | A0     | tSAS   |           | 150       | —    |      |

| Address hold time   |        | tSAH   |           | 150       | _    |      |

| Data setup time     | SI     | tSDS   |           | 100       | —    | 7    |

| Data hold time      |        | tSDH   |           | 100       | _    |      |

| CS-SCL time         | CS     | tCSS   |           | 150       | —    |      |

|                     |        | tCSH   |           | 150       |      |      |

#### [VDD=1.8V to 2.7V, Ta=-40 to 85°C]

| Item                | Circul | Cumhal | Condition | Specifica | Specification value |        |

|---------------------|--------|--------|-----------|-----------|---------------------|--------|

|                     | Signal | Symbol | Condition | Min.      | Max.                | - Unit |

| Serial clock cycle  | SCL    | tSCYC  |           | 400       | —                   | ns     |

| SCL "H" pulse width |        | tshw   |           | 150       | _                   |        |

| SCL "L" pulse width |        | tsLw   |           | 150       | _                   |        |

| Address setup time  | A0     | tsas   |           | 250       | _                   | _      |

| Address hold time   |        | tSAH   |           | 250       | _                   |        |

| Data setup time     | SI     | tSDS   |           | 150       | —                   | _      |

| Data hold time      |        | tSDH   |           | 150       | _                   |        |

| CS-SCL time         | CS     | tCSS   |           | 250       | —                   | _      |

|                     |        | tCSH   |           | 250       | _                   |        |

Notes: 1. The rise and fall times (tr and tf) of the input signal are specified for less than 15 ns. 2. All timings are specified based on the 20 and 80% of VDD.

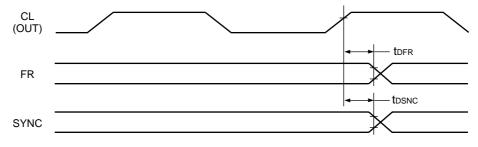

#### Display control output timing

#### [VDD=4.5V to 5.5V, Ta=-40 to 85°C]

| ltem            | Signal        | Symbol        | nbol Condition | Sp   | Unit |      |    |

|-----------------|---------------|---------------|----------------|------|------|------|----|

|                 | Signal Symbol | Condition     | Min.           | Тур. | Max. | Unit |    |

| FR delay time   | FR            | tDFR          | C∟=50pF        |      | 10   | 40   | ns |

| SYNC delay time | SYNC          | <b>t</b> DSNC | C∟=50pF        | —    | 10   | 40   | ns |

[VDD=2.7V to 4.5V, Ta=-40 to 85°C]

| Item            | Signal        | Signal Symbol | Condition | Sp   | Unit |      |    |

|-----------------|---------------|---------------|-----------|------|------|------|----|

|                 | Signal Symbol | Condition     | Min.      | Тур. | Max. | Unit |    |

| FR delay time   | FR            | tDFR          | C∟=50pF   | —    | 20   | 80   | ns |

| SYNC delay time | SYNC          | <b>t</b> DSNC | CL=50pF   |      | 20   | 80   | ns |

[VDD=1.8V to 2.7V, Ta=-40 to 85°C]

| Item            | Signal Syml | Symbol        | Symbol    | Symbol | Condition | Sp   | ecification va | lue | Unit |

|-----------------|-------------|---------------|-----------|--------|-----------|------|----------------|-----|------|

|                 |             | Symbol        | Condition | Min.   | Тур.      | Max. | Unit           |     |      |

| FR delay time   | FR          | tDFR          | C∟=50pF   | _      | 50        | 200  | ns             |     |      |

| SYNC delay time | SYNC        | <b>t</b> DSNC | CL=50pF   |        | 50        | 200  | ns             |     |      |

Notes: 1. Valid only when the master mode is selected.

All timings are specified based on the 20 and 80% of VDD.

Pay attention not to cause delays of the timing signals CL, FR and SYNC to the salve side by wiring resistance, etc., while master/slave operations are in progress. If these delays occur, indication failures such as flickering may occur.

## **SED157A Series**

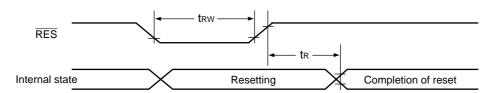

#### • Reset input timing

[VDD=4.5V to 5.5V, Ta=-40 to 85°C]

|                       | <u>.</u>      |        | Symbol Condition | Spe  |      |      |      |

|-----------------------|---------------|--------|------------------|------|------|------|------|

| ltem                  | Signal Symbol | Symbol |                  | Min. | Тур. | Max. | Unit |

| Reset time            |               | tR     |                  | —    | —    | 0.5  | μs   |

| Reset "L" pulse width | RES           | trw    |                  | 0.5  | _    | —    |      |

[VDD=2.7V to 4.5V, Ta=-40 to 85°C]

|                       |        |        | Spe       |      |      |      |      |

|-----------------------|--------|--------|-----------|------|------|------|------|

| ltem                  | Signal | Symbol | Condition | Min. | Тур. | Max. | Unit |

| Reset time            |        | tR     |           | —    | _    | 1    | μs   |

| Reset "L" pulse width | RES    | trw    |           | 1    | _    | —    |      |

[VDD=1.8V to 2.7V, Ta=-40 to 85°C]

|                       | <u>.</u> |        |           | Sp   |      |      |      |

|-----------------------|----------|--------|-----------|------|------|------|------|

| ltem                  | Signal   | Symbol | Condition | Min. | Тур. | Max. | Unit |

| Reset time            |          | tR     |           | _    |      | 1.5  | μs   |

| Reset "L" pulse width | RES      | trw    |           | 1.5  | —    | —    |      |

Note: All timings are specified based on the 20 and 80% of VDD.

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2000 All right reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

#### SEIKO EPSON CORPORATION

ELECTRONIC DEVICES MARKETING DIVISION

#### IC Marketing & Engineering Group

**ED International Marketing Department I (Europe, U.S.A)** 421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5812 FAX: 042-587-5564

**ED International Marketing Department II (ASIA)** 421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5110 Electronic devices information on the Epson WWW server. http://www.epson.co.jp/device/

First issue February, 2000 Printed in Japan (I)